Processor: 1517F3; Software: TIAPV13. Application scan time: 1mS.

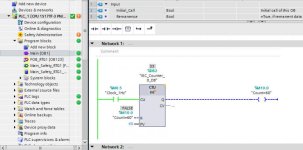

I have several FCs which are unconditionally called in OB1. In one of them there is a CTU instruction which is incremented by the system clock 1Hz bit, M0.5. There are other conditions in the rung to permit counting; these are all stable and set on.

The counter is incrementing erratically. The net result is that a 30s preset completes in 15s.

I have tried each of the following to find the cause:

1: changed the M0.5 XIC to a positive differentiating XIC.

2: inserted a Ptrig in the rung after the clock bit.

3: removed all other conditions in the rung.

4: set up a CTU in OB1, incremented by M0.5 (with and without the Ptrg).

Needles to say, it has persisted or I wouldn't be typing this.

In order to check the integrity of the M0.5 bit, I configured it to enable an unused output. First thing I noticed was that it was not 1:1 on/off, but also that it was running consistently slow: about 0.75Hz.

What an I doing wrong here??? Thank you.

I have several FCs which are unconditionally called in OB1. In one of them there is a CTU instruction which is incremented by the system clock 1Hz bit, M0.5. There are other conditions in the rung to permit counting; these are all stable and set on.

The counter is incrementing erratically. The net result is that a 30s preset completes in 15s.

I have tried each of the following to find the cause:

1: changed the M0.5 XIC to a positive differentiating XIC.

2: inserted a Ptrig in the rung after the clock bit.

3: removed all other conditions in the rung.

4: set up a CTU in OB1, incremented by M0.5 (with and without the Ptrg).

Needles to say, it has persisted or I wouldn't be typing this.

In order to check the integrity of the M0.5 bit, I configured it to enable an unused output. First thing I noticed was that it was not 1:1 on/off, but also that it was running consistently slow: about 0.75Hz.

What an I doing wrong here??? Thank you.