timbo_uk

Member

Hi there,

(Actually a continuation of this thread (http://www.plctalk.net/qanda/showthread.php?t=47163) but title not really getting attention.

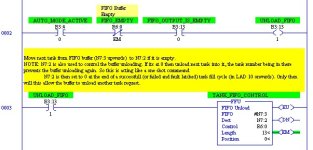

I am trying to work out why this bit of code is not working as expected.

Basically I am trying to empty a FIFO buffer (numbers of tanks that need filling up) starting at N7:3 and 13 integers long into N7:2.

The trigger to unload is supposed to be when N7:2 is empty. The idea behind this is: tank requests to be filled, tank number is added to FIFO buffer, first request unloaded from buffer into N7:2, N7:2 is used to call the particular tanks fill subroutine, when finished that routine writes "0" into N7:2, it should then repeat the sequence.

The bit of code below never unloads the FIFO even when N7:2 is at zero.

By trial and error I have found I can make it work by adding a bit triggered from the free running clock (S4:12) onto rung 0001 between the EQU and the bit output. It works perfectly as expected then.

Can anyone see why this is? I am a bit of a novice self taught programmer, so not sure of the "nitty gritty" going on during the scan.

The full (work in progress) project can be downloaded from the end of the topic linked too at the top of this post.

Hopefully somebody can tell me why, and suggest ways around it

Thanks

(Actually a continuation of this thread (http://www.plctalk.net/qanda/showthread.php?t=47163) but title not really getting attention.

I am trying to work out why this bit of code is not working as expected.

Basically I am trying to empty a FIFO buffer (numbers of tanks that need filling up) starting at N7:3 and 13 integers long into N7:2.

The trigger to unload is supposed to be when N7:2 is empty. The idea behind this is: tank requests to be filled, tank number is added to FIFO buffer, first request unloaded from buffer into N7:2, N7:2 is used to call the particular tanks fill subroutine, when finished that routine writes "0" into N7:2, it should then repeat the sequence.

The bit of code below never unloads the FIFO even when N7:2 is at zero.

By trial and error I have found I can make it work by adding a bit triggered from the free running clock (S4:12) onto rung 0001 between the EQU and the bit output. It works perfectly as expected then.

Can anyone see why this is? I am a bit of a novice self taught programmer, so not sure of the "nitty gritty" going on during the scan.

The full (work in progress) project can be downloaded from the end of the topic linked too at the top of this post.

Hopefully somebody can tell me why, and suggest ways around it

Thanks