learner

Lifetime Supporting Member

Hi,

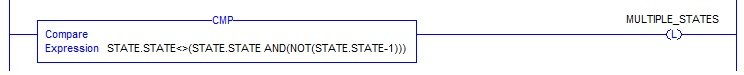

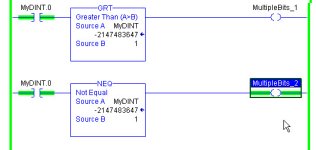

I have 10 bits in OR configuration. any of this bits could be on at anytime based on a certain condition. however I can't have two or more bits to be on at the same time. I am looking for a logic to help me detect the situation that two or more bits will turn the OTE on. In case this help, these 10 bits are Valid paths for a process but only one valid path at a time must exist.

Thank you

I have 10 bits in OR configuration. any of this bits could be on at anytime based on a certain condition. however I can't have two or more bits to be on at the same time. I am looking for a logic to help me detect the situation that two or more bits will turn the OTE on. In case this help, these 10 bits are Valid paths for a process but only one valid path at a time must exist.

Thank you