RogerBrunner

Member

I have a program that has been functioning great and now would like to add an additional feature. Currently the program is based on timing, timing is next to impossible to control in this situation.

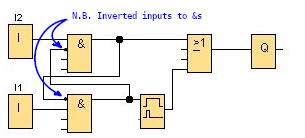

The current flaw, if I1 is active and I2 process goes active it overrides the I1 process. Ideally I would like I2 not to take over until I1 has cleared, however as soon as I1 clears it will go active within a few seconds and at this point I2 can run process.

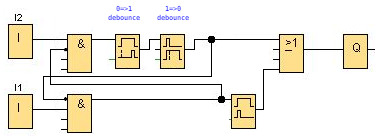

This is where I think counters would be better vs timers. Run the I2 process for 3 counts at I1 and then reset.

The current flaw, if I1 is active and I2 process goes active it overrides the I1 process. Ideally I would like I2 not to take over until I1 has cleared, however as soon as I1 clears it will go active within a few seconds and at this point I2 can run process.

This is where I think counters would be better vs timers. Run the I2 process for 3 counts at I1 and then reset.