Hi,

I recently had an incident with a program that was written in STL. It went like this:

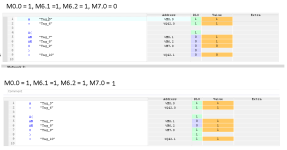

A M0.0

= Q42.0

A(

AN M6.1

AN M6.2

O M7.0

)

= Q42.1

When we ran the program I noticed that M7.0 changed status based on the RLO coming from Q42.0, and not by the conditions for M7.0, which were written in other part of the program. M6.1 and M6.2 did not change, so the only thing that changed when we ran program was Q42.0, and it had impact on condition of M7.0.

So I wrote CLR on the line after =Q42.0, and above A(, and the logic worked as intended.

So to me it seems that when one writes this code in STL one has to be cautious about the RLO from previous instructions in the code. Is this considered a bug?

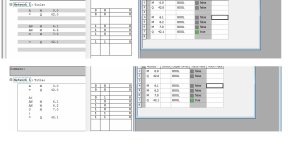

What happens if I write this in ladder or function? Will simatic manager insert the necessary handling of RLO so that the code does what it is supposed to do?

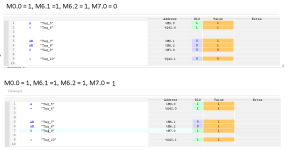

I recently had an incident with a program that was written in STL. It went like this:

A M0.0

= Q42.0

A(

AN M6.1

AN M6.2

O M7.0

)

= Q42.1

When we ran the program I noticed that M7.0 changed status based on the RLO coming from Q42.0, and not by the conditions for M7.0, which were written in other part of the program. M6.1 and M6.2 did not change, so the only thing that changed when we ran program was Q42.0, and it had impact on condition of M7.0.

So I wrote CLR on the line after =Q42.0, and above A(, and the logic worked as intended.

So to me it seems that when one writes this code in STL one has to be cautious about the RLO from previous instructions in the code. Is this considered a bug?

What happens if I write this in ladder or function? Will simatic manager insert the necessary handling of RLO so that the code does what it is supposed to do?