drbitboy

Lifetime Supporting Member

Good morning (EST),

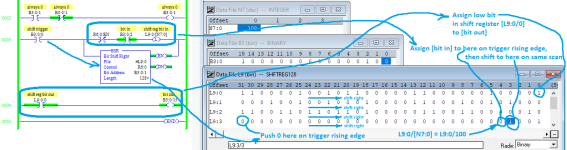

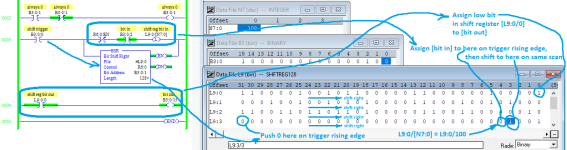

I am trying to implement the code below in on an S7-1200. It's barely half a dozen instructions, but I am stuck; I have not even been able to figure out how to conveniently access a bit in a DINT (still searching though; surely it's possible? Yes, and don't call me Shirley ). I'm almost to the point of building an FB equivalent to A-B's BSR instruction.

). I'm almost to the point of building an FB equivalent to A-B's BSR instruction.

I'm sure it's just unfamiliarity with TIA and Siemens notation.

If interested, could someone please post TIA LAD code equivalent to the image below, including showing the DB entries. The key behaviors are

Thanks,

Brian Carcich

P.S. this is only for thread https://www.plctalk.net/qanda/showthread.php?t=128167

I am trying to implement the code below in on an S7-1200. It's barely half a dozen instructions, but I am stuck; I have not even been able to figure out how to conveniently access a bit in a DINT (still searching though; surely it's possible? Yes, and don't call me Shirley

I'm sure it's just unfamiliarity with TIA and Siemens notation.

If interested, could someone please post TIA LAD code equivalent to the image below, including showing the DB entries. The key behaviors are

- shift register with 128 bits using an array of DINTs (e.g. ARRAY[0..3] of DINT; or UDInts or DWords, or even Bools for that matter)

- on a rising edge of a trigger bit, shift all members of the shift_reg array by 1 bit to the right, cascading bit 0 of shift_reg[N] to bit 31 of shift_reg[N-1] for N > 1

- and push a zero bit onto shift_reg[3] at bit 31 (128th MSBit)

- and latch bit of the shift register when some input [bit it] is 1, where I is a non-constant tag with a value between 1 and 127 inclusive.

- bit = bit [I AND 31] of shift_reg[(I AND (-32))/32]; -32 is 16#FFE0 (16-bit signed int)

[*]So if I is 100, then bit 4 of shift_reg[3]

- bit = bit [I AND 31] of shift_reg[(I AND (-32))/32]; -32 is 16#FFE0 (16-bit signed int)

[*]output bit 0 of shift_reg[0] continuously

Thanks,

Brian Carcich

P.S. this is only for thread https://www.plctalk.net/qanda/showthread.php?t=128167