Long time lurker, first time poster..

I've been working with PLCs for a while now and have ran into a head scratcher that I was hoping someone (smarter than I) could shed some light on for me.

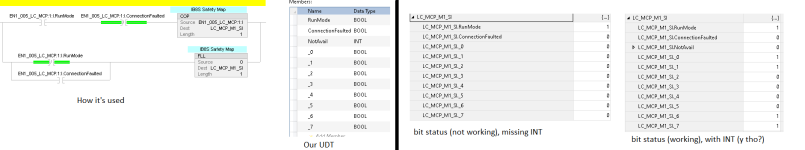

We have a UDT created to map 1734-IB8S cards into the same format as our schematics. This UDT is a series of separate BOOLs that make up the RunMode, ConnectionFaulted, and 0-7 for the Data (status omitted). Making a total of 10 bits in our UDT. The tag created from the hardware has 18 bits.

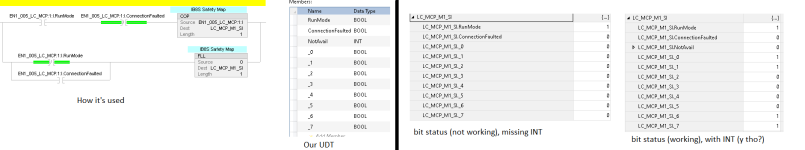

We then use a COP to try to grab these first 10 bits but the only thing that works is adding an INT between the Connection faulted and the first data point in our UDT.

Is anyone aware of why we would need that dummy INT for this to copy properly? Doesn't seem to line up to me.. I would like to understand WHY it works so I can be confident it is a valid fix.

I've been working with PLCs for a while now and have ran into a head scratcher that I was hoping someone (smarter than I) could shed some light on for me.

We have a UDT created to map 1734-IB8S cards into the same format as our schematics. This UDT is a series of separate BOOLs that make up the RunMode, ConnectionFaulted, and 0-7 for the Data (status omitted). Making a total of 10 bits in our UDT. The tag created from the hardware has 18 bits.

We then use a COP to try to grab these first 10 bits but the only thing that works is adding an INT between the Connection faulted and the first data point in our UDT.

Is anyone aware of why we would need that dummy INT for this to copy properly? Doesn't seem to line up to me.. I would like to understand WHY it works so I can be confident it is a valid fix.

Last edited: