Hi Guys,

I'm having a weird problem that I don't understand.

The problem is that a bit needs to be transferred via DP/DP coupler with a sensor event. The bit can be transferred a 100 times without issues and fails then one time, the failmoment is random and doen't happen often but is a big issue for the production.

After making logs plc based (SCL and fifo tables) showed on WinCC I could see that the problem came from the sender PLC. So I started placing counters on every possible condition and action. The thing is that the cause is a Set Reset function.

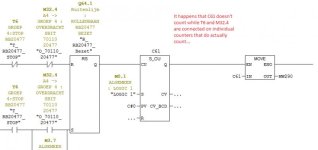

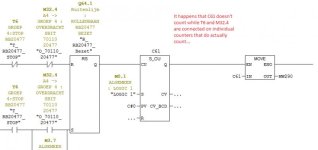

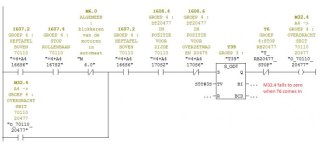

It happens that C61 misses Q64.1 while it should be setted. I have counters on the T6 signal and M32.4 also, they both count ??? Ok the moment can be different... But that's impossible if you look at the next network. In this network we allready made it a RS instead of a SR just as a test and since then the problem didn't happen again...??

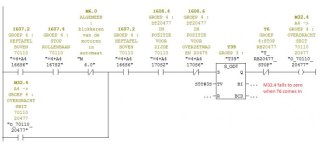

Here you can see that M32.4 is stopped by T6. T6 is a on delay timer from a sensor input. This network is processed later then the previous one, so the combination T6 + M32.4 should allways bin there. So still, why is it possible that C61 doesn't count sometimes ?

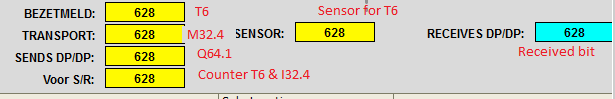

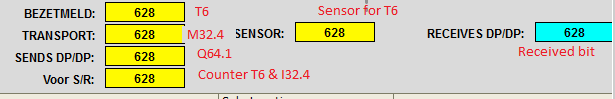

These are my counters on WinCC:

No data is used double, I've checked that many times allready, not in Scada, not on HMI's.

Any help is appruciated a lot,

Thanks,

Kind regards,

Gerry

I'm having a weird problem that I don't understand.

The problem is that a bit needs to be transferred via DP/DP coupler with a sensor event. The bit can be transferred a 100 times without issues and fails then one time, the failmoment is random and doen't happen often but is a big issue for the production.

After making logs plc based (SCL and fifo tables) showed on WinCC I could see that the problem came from the sender PLC. So I started placing counters on every possible condition and action. The thing is that the cause is a Set Reset function.

It happens that C61 misses Q64.1 while it should be setted. I have counters on the T6 signal and M32.4 also, they both count ??? Ok the moment can be different... But that's impossible if you look at the next network. In this network we allready made it a RS instead of a SR just as a test and since then the problem didn't happen again...??

Here you can see that M32.4 is stopped by T6. T6 is a on delay timer from a sensor input. This network is processed later then the previous one, so the combination T6 + M32.4 should allways bin there. So still, why is it possible that C61 doesn't count sometimes ?

These are my counters on WinCC:

No data is used double, I've checked that many times allready, not in Scada, not on HMI's.

Any help is appruciated a lot,

Thanks,

Kind regards,

Gerry