Hi,

I have an odd issue.

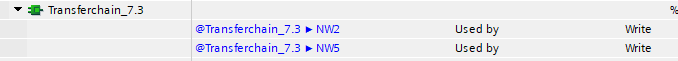

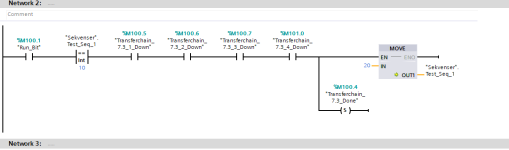

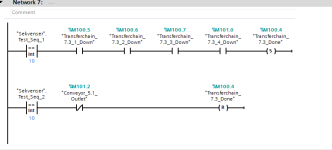

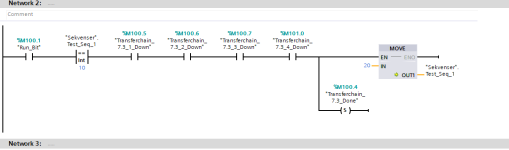

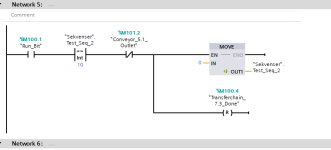

I use the S/R instruction to enable another step to be executed in the program.

And when "Test_Seq_2" becomes 10, "Transferchain_7.3_Done" should go "False".

Sometimes this work, sometimes the "Set" keeps hanging.

The "Test_Seq_2" becomes "0", but the "Transferchain_7.3_Done" is still "True".

And "Test_Seq_1" is not in Step 10 when i am trying to reset the bit.

Could this be some scan-related issue?

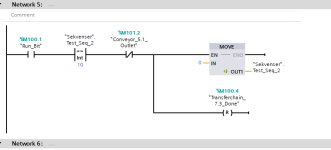

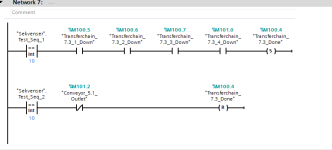

And for good measure.

Same result as the above.

I have an odd issue.

I use the S/R instruction to enable another step to be executed in the program.

And when "Test_Seq_2" becomes 10, "Transferchain_7.3_Done" should go "False".

Sometimes this work, sometimes the "Set" keeps hanging.

The "Test_Seq_2" becomes "0", but the "Transferchain_7.3_Done" is still "True".

And "Test_Seq_1" is not in Step 10 when i am trying to reset the bit.

Could this be some scan-related issue?

And for good measure.

Same result as the above.

Last edited: