The little devil on my left shoulder is saying: “Go ahead – let’s play hardball”. The little angel on my other shoulder is saying: “Don’t do it, Ron – you’ll scare the children”. Well, some of the beginners in the audience may have to sleep with the lights on tonight – but here goes anyway.

David_Emmerich made an interesting observation in post #24:

I always pick a 'spare'input address way up above my used i/o limit and label it "DUMMY". then if I need to 'short' or test a rung or lock out arung at any time I just insert 'Dummy'. Work great. And if you want to turn on the test area or what ever, just force on your ' Dummy' bit.

No offense David, but personally I’m going to stick with my “series” or “parallel” constructions for “always off” and “always on” test conditions (as mentioned in my post #22). Let me show you why and see if you agree.

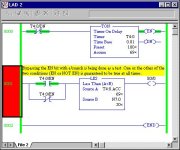

WARNING! The following program may be disturbing to young viewers. [attachment]

This is one of my many infamous “hardball” programs which I often use to demonstrate to beginners what REALLY goes on inside the PLC as it scans its program. It may not be a pretty picture – but it’s HIGHLY educational when followed all the way through its analysis. (You may interpret that as: “You ain’t seen nothin’ yet.”) So you see, even an UNWIRED input bit can be highjacked by a simple typographical error. (I actually stumbled across this phenomenon late one evening when one of my students accidentally typed in “I:011/5” instead of “O:011/5” as an address for an OTE). So based on all of this, I still like my old tried-and-true “series” and “parallel” test constructions. If THOSE ever fail, I’ll have to change careers.

And a quick note to our distinguished colleague 93lt1 (who, like myself) apparently has much more familiarity with the PLC-5 and SLC-500 platforms. We have to keep remembering that the guys in this thread are playing around with a MicroLogix-1500. The forces are ALWAYS enabled in this simpler processor. I got burned with my “unconditional” test branch (see posts #8 and #18) so I’m trying to be more careful now. It’s not easy moving into the “cheap seats” - but I’m trying to fit in.

Finally, an IMPORTANT note to all (and especially to Jim Davis – who seems to have a true appreciation for real-world programming techniques) – the material in THIS particular post is intended solely for educational purposes. I certainly do NOT recommend using these “Twilight Zone” procedures for real-world programs. I will, however, stick by my (well, actually by John’s) flasher solution of “one timer – and a LES (less-than) comparison” though. And yes, I’ll certainly agree that the GRT (greater-than) - which my incessant goading forced him to add - IS overkill. That too was purely for educational purposes.

And really finally, for those who are interested in the apparently “dirt simple” AFI from the PLC-5 instruction set, this is a direct quote from the RSLogix5 online help file:

This input instruction disables its rung when inserted in the condition side of the rung. Use for debugging programs and for temporarily deactivating a rung that will be needed later. Program an AFI as the first input in the rung. © 1997 Rockwell Software Inc.

I say that there are three (yes, I said “three”) errors in that short official description. This isn’t intended to knock the Rockwell Software developers, of course, but I think that our beginners need to know the facts. As jthornton said in another thread: "Inquiring minds want to know...."