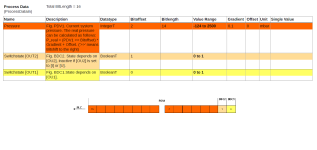

RS 500 ML1400: Mov and shift by 2 bits right

- Thread starter theColonel26

- Start date

Similar Topics

I have a Allen Bradely 1500 that has a cracked board. It still works but needs replaced (battery is no longer connected). To make migration easier...

Hello,

I have an AB MicroLogix PLC (1400 1766-L32BWA), and I want to communicate with the SLC500 PLC (1747-L40C)

has any of you already done so...

Hi All. I can write an N7 value to a modbus register in an Automation Direct Servo but I can't read a holding register to an N7 address. I've...

I need to do 5 reads and 1 write on 2 devices. So that is 10 and 2 total.

It seems I can't use indirect addressing with MG registers, which is...

Hey guys

I created a data filed called N7 for some integers

I want to now remove it. Im off line and just working on something at home.

RS500...