There must be a way to read in a stream of good/bad reject status at one PE and then act on the reversed stream leaving the other PE right before the reject conveyor...

You don't have to reverse anything; use BSR so the bit of interest to every downstream PE2 event is popped off the FIFO from position FIFO[0]; also, you are going to have 0-valued bits in the FIFO for every non-reject, not-to-be-diverted box as well. In other words, there will be one bit in the FIFO per tracked box. Also, you do not put the 1- or 0-valued bit at the head of the FIFO with the BSR, you put a 0-valued bit there and change it later when it is closer to the tail of the FIFO. Also, the PE2 event triggers the BSR; the PE1 event does not trigger a BSR. It could be done the other way, but the concept is the same.

Details

The key is that there is a bit in the FIFO for every tracked box, whether rejected or not, plus some extra bits for un-tracked upstream boxes that have not yet hit PE1.

A tracked box is a box that has triggered PE1 but not yet PE2.

The FIFO of bits is bigger than the number of tracked boxes.

The BSR triggered by a downstream PE2 event adds add a 0-valued (future box is assumed okay - for now) bit at the head of the FIFO i.e. bit index 63 in the FIFO, and that index 63 is way beyond any tracked box the system will ever see, so it represents a future box that has not yet made it to PE1.

You also keep track of number of tracked boxes in the range [PE1

E2), we call it BIT_INDEX_AT_PE1.

Then one of two things happens:

1) A new box triggers the PhotoEye PE1

1.1) If that box is a reject, rite a 1-valued bit for that new box at index BIT_INDEX_AT_PE1 of the FIFO

1.2) Increment BIT_INDEX_AT_PE1, to maintain the model of the number of boxes in the range [PE1

E2).

N.B. in our latest implementation REJECT_TRACKING_B.RSS, we reverse those two steps and do the increment via CTU first, which means the bit that is written is at index (BIT_INDEX_AT_PE1 - 1).

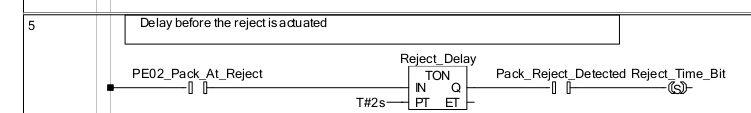

2) The next box to divert, or to not divert, triggers the PhotoEye PE2

2.1) Pop (BSR) the oldest bit from tail of the FIFO

2.1.1) If that popped bit is a 1, divert that next box

2.1.2) If that popped bit is a 0, do not divert that next box

2.2) Decrement BIT_INDEX_AT_PE1

Say index BIT_INDEX_AT_PE1 is zero, so there are no tracked boxes, and a box A triggers PE1*. At that time, the reject input is 0 (box A is okay and not a reject, and it should not be diverted). So you leave FIFO[0]=FIFO[BIT_INDEX_AT_PE1]=0 and increment the index to 1.

Then a box B triggers PE1, but the reject input is 1 so box B is a reject and should be diverted. So you latch FIFO[1]=FIFO[BIT_INDEX_AT_PE1]=1 and incrment the index to 2 (two tracked boxes).

Note that you did not trigger a BSR for either PE1 event; you only wrote a bit into the FIFO somewhere after the head of the FIFO.

Then box A triggers PE2: you trigger the BSR to pop the zero from FIFO[0] and shift the rest of the bits down 1, so FIFO[0] becomes 1. You decrement BIT_INDEX_AT_PE1 to 1, and the popped zero tells you to not divert box A.

Then box B triggers PE2: you trigger the BSR to pop the 1 from FIFO[0] (placed there by the previous BSR for box A) and shift the rest of the bits down 1. You decrement BIT_INDEX_AT PE1 to 0 (no more tracked boxes), and the popped one tells you to divert box B.

So there are only two events: new box triggers PE1; tracked box triggers PE2.

The rest is housekeeping: increment or decrement BIT_INDEX_AT_PE1 so you know how many tracked boxes there are and where the next okay/reject bit goes in the FIFO; write a bit at FIFO[BIT_INDEX_AT_PE1] for a new box or pop (BSR) a bit from the tail of the FIFO to tell you what to do for a box that just triggered PE2.

* nothing can hit PE2 at that point, because the index is 0 so there are no tracked boxes, and a box has to trigger PE1 before it can trigger PE1

) branches.