...This process repeats every time the rung goes from false to true ... And the rung must return back to false to start the next shift. ...

Just to muddy the waters (so don't read this until you complete GaryS's post fully):

A more specific way to state this is that the process repeats when

- The BSL input rung is true

- AND

- The CONTROL.EN bit is 0

Also, whenever the BSL input rung is true or false, the CONTROL.EN bit will be assigned 1 or 0, respectively, each time the BSL instruction rung executes.

That is, the [BSL input rung + the CONTROL.EN bit] compose a one-shot, where the CONTROL.EN bit is equivalent to the storage bit of a one-shot instruction (e.g. ONS or OSR).

So strictly speaking, to have the BSL do the next shift, either

- In the normal case the input rung has to return back to false and then true again i.e. rising edge, as noted by GaryS

- OR

- In a special case the CONTROL.EN bit has to be assigned 0, so on the next scan the input rung still-true state will appear to be a rising edge.

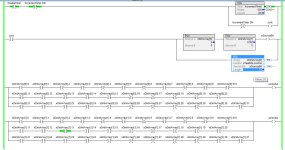

See below; when L10:0/7 (L10:0=128) is 1 and that 1 is shifted to L10:0/8 (L10:0=256), the next 7 BSL shifts will occur on the next 7 scans because Rung 0003 will clear CONTROL.EN after the BSL, so the BSL will detect a rising edge condition, on those next 7 scans, until the 1 bit gets to L10:/15 (L10:0=65536).