according to this website:http://www.plcs.net/chapters/respdetails6.htm, the input should be on for at least 1 input delay time + one scan time in order for the processor to reliably read the input.

I don't see why the extra "1 input delay time" is needed. Let say the scan cycle consists of read input, prog exec and update output task. Lets assume that each operation takes 1ms. If so, then the sample rate of the input performed by the processor would be 1/3ms or 333.3 Hz.

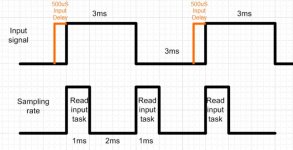

According to classic signal sampling rule, the sampling rate should be twice as fast as the rate of the signal being sampled. Thus a 333.3 Hz sampling rate is suitable for sampling a signal that is 166.6hz or lower. A 166.6hz signal has pulses with a 3ms duration, which is the same duration of the PLC scan cycle. The graph below obeys the sampling rule but the input signal's doesn't have the extra "1 input delay time"

I don't see why the extra "1 input delay time" is needed. Let say the scan cycle consists of read input, prog exec and update output task. Lets assume that each operation takes 1ms. If so, then the sample rate of the input performed by the processor would be 1/3ms or 333.3 Hz.

According to classic signal sampling rule, the sampling rate should be twice as fast as the rate of the signal being sampled. Thus a 333.3 Hz sampling rate is suitable for sampling a signal that is 166.6hz or lower. A 166.6hz signal has pulses with a 3ms duration, which is the same duration of the PLC scan cycle. The graph below obeys the sampling rule but the input signal's doesn't have the extra "1 input delay time"

Last edited: