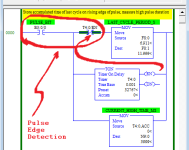

Here is a minimal approach using RSLogix 500 (Micro Starter Lite; see LAD 3 MEASURPULS on the right; the rest is for simulation and testing). RSLogix 5000 would be similar, although the timers could count to 2Ms+ (two billion milliseconds).

This code shows

Those values could be displayed in an HMI; other values and/or quantities and/or units could also be calculated and displayed e.g. a bar chart of the last 10-20 cycle times.

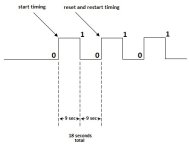

- F8:1 - the last total cycle time i.e. the elapsed time between the last two rising edges, s, float;

- F8:0 - the elapsed time into the current cycle i.e. since the last rising edge of the pulse, s, float;

- N9:1 - the elapsed time of the pulse signal being high during the current cycle, ms, integer;

- N9:2 - the elapsed time of the pulse signal being low during the current cycle, ms, integer;

- the state of the pulse (1=high; 0=low).

CaveatThe time values are not exact as they lose a scan cycle here and there, but as that is only a few ms out of several seconds, I suspect that is acceptable.View attachment 66589

thank you so much, let me see if I can wrap my head around this. It's been a while since I've looked at RSLogix 500 logic.