allscott

Member

- Join Date

- Jul 2004

- Posts

- 1,332

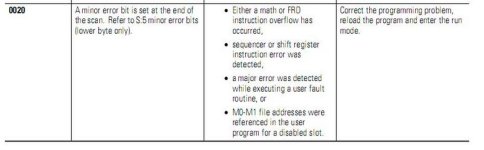

I just had a SLC 5/05 fault on a major error. The error code was 20H which according to the manual says "A minor error bit is set at the end of the scan. This recoverable error occurs at run time."

Can anyone tell me what this means or where to go to find more information on this fault?

Can anyone tell me what this means or where to go to find more information on this fault?