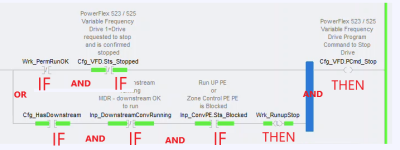

How does that rightmost AND work?? Wouldn't that not turn on the coil?

This is referencing the graphic originally included on post #11 and included again here. Starting on the left with the top of the branch. Let's sound out how this would be scanned.

IF Wrk_PermRunOK =

OFF/OPEN AND IF Cfg_VFD.Sts_Stopped =

OFF/OPEN THEN Cfg_VFD.PCmd_Stop =

ON

OR (Now we move to the lower level of the branch)

IF Cfg_HasDownstream =

ON/CLOSED AND IF Inp_DownstreamConvRunning =

OFF/OPEN AND IF InpConvPE.Sts_Blocked =

ON/CLOSED THEN Wrk_RunupStop = ON AND [/COLOR][B

]Cfg_VFD.PCmd_Stop[/B] =

ON

So, if the top portion of the rung is true, the OTE energizes and the OTL takes no action. It doesn't turn on or off. It is left in its current state. If the bottom portion of the branch is true, then the OTL will energize and then the OTE will also energize.

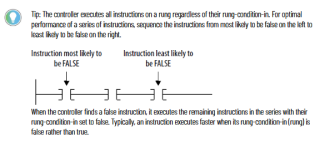

Now, a bit off the topic, but we know people refer to these posts years down the track, I would disagree ever so slightly with the comment I_Automation made that Logix 5000 scans all instructions. That is a little misleading. Let me explain....

Let's assume that the top rung is true. The bottom portion does not get scanned. Not in a 5, not the 500, nor in a 5000. I taught all of these controllers for Rockwell for 20+ years. If I am mistaken, please show me where this is documented. Wouldn't be the first time I was wrong.

Now, let's assume that the first instruction on the top branch is false. We then stop scanning that branch. BUT, and this is a BIG BUT, only because there is no output to the right within the left and right legs of the branch. There is one further to the right, but it is outside the branch legs.

Now, let's just say that there WAS an output inside the branch, just like on the bottom branch level. If that was the case, when the scan determines that the left most instruction is false, that sets the rung state to false, and we continue to the right to the next instruction. When it reaches that second instruction it will not take the time to evaluate whether the instruction is true. Instead it executes it as false and continues to the right where our new output would be. It would then set that output to a false state. It must continue scanning through that false logic in order to set the output to false.

Next lets go back to assuming the logic is as written and that top level is false. But let's assume that the first instruction in the bottom branch is false while the other inputs are true. As the scan moves from left to right, here is how I describe it. "False, don't care, don't care, set the OTL to false". Even though the first instruction was false, it must continue scanning the instructions so it can set the OTL to false and then exit the branch and also set the OTE to false.

All of this true for the 5, 500, and the 5000. The difference of course being that the 5/500 models don't support series outputs.

OG