Situation:

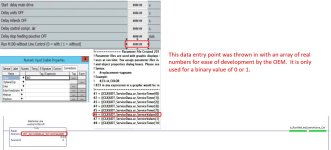

Single [EQU] instruction with single [OTE] on a rung, nothing else/simple. [EQU] operand(A) is a real number data type. Operand(B) is fixed value "0".

Result:

[EQU] sometimes executes as false when the value of the real number looks to be "0.0"

Question:

Does the CLGX execute the [EQU] in such a way that what I'm witnessing makes sense?

I'm probably going to move the real# into a DINT, then change the operand of the [EQU] to the DINT tag. This will work because the REAL# is being used by the OEM to reflect a binary state (interlock on/off). I think they just lumped this data into an array of real numbers where it didn't belong.

Single [EQU] instruction with single [OTE] on a rung, nothing else/simple. [EQU] operand(A) is a real number data type. Operand(B) is fixed value "0".

Result:

[EQU] sometimes executes as false when the value of the real number looks to be "0.0"

Question:

Does the CLGX execute the [EQU] in such a way that what I'm witnessing makes sense?

I'm probably going to move the real# into a DINT, then change the operand of the [EQU] to the DINT tag. This will work because the REAL# is being used by the OEM to reflect a binary state (interlock on/off). I think they just lumped this data into an array of real numbers where it didn't belong.