OWEN.DAVID

Member

In my mind there is a clear rationale to favour the use of input map routines with compactlogix controllers.

The inputs are updated asynchronously to the scan cycle and an Alias tag which refers directly to an input card may update its value part way through a routine and lead to instability.

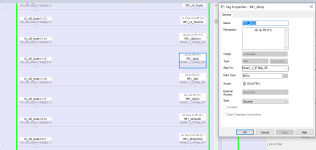

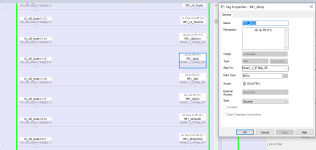

However, I am confused as to why a project would have input map routines that map the inputs to the tags that are already aliasing the same input. The screenshot shows this clearly.

My understanding of this logic is that we are updating the tag value once in the input map and then again (possibly more than once) when the inputs update asynchronously at some point during the scan. This seems to be an example of poor project design and I believe it should be changed.

One likely explanation for this is that the project file was created in 2012/2013 using a version of logix 20 or below. Similarly the project was created at this time by a automation specialist and was then handed over to a non-specialist company who have updated the controller, logix version, and code over time.

I am now in the position to do some housekeeping to improve the code base and wonder what the best practice is?

*To convert all of the alias tags to base tags and then retain the input map at the start of the scan cycle

or

*To use the parameter functionality in Studio5000 and remove the input maps entirely.

Thoughts and comments would be very welcome, especially if there is something hiding in plain wrt best practices for input mapping.

Thanks

The inputs are updated asynchronously to the scan cycle and an Alias tag which refers directly to an input card may update its value part way through a routine and lead to instability.

However, I am confused as to why a project would have input map routines that map the inputs to the tags that are already aliasing the same input. The screenshot shows this clearly.

My understanding of this logic is that we are updating the tag value once in the input map and then again (possibly more than once) when the inputs update asynchronously at some point during the scan. This seems to be an example of poor project design and I believe it should be changed.

One likely explanation for this is that the project file was created in 2012/2013 using a version of logix 20 or below. Similarly the project was created at this time by a automation specialist and was then handed over to a non-specialist company who have updated the controller, logix version, and code over time.

I am now in the position to do some housekeeping to improve the code base and wonder what the best practice is?

*To convert all of the alias tags to base tags and then retain the input map at the start of the scan cycle

or

*To use the parameter functionality in Studio5000 and remove the input maps entirely.

Thoughts and comments would be very welcome, especially if there is something hiding in plain wrt best practices for input mapping.

Thanks