You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

tlibby

- Thread starter troylibby

- Start date

Mickey

Lifetime Supporting Member

Bobbias

Member

It depends. If there's anything in the program that relys on how the modicon scans, then yes, it would actually matter.

jstolaruk

Lifetime Supporting Member

You'll first have to review the original code to see if there is anything that is scan specific, mostly one shots. Then look for ladder code that uses bits grouped into integers; the programmer may have had some kind of coding involved there that looks at these integers after the ladders have worked on the bits. Also look for Modicon specific instructions that are not offered by AB;you'll probably have to code something in simple ladder that replicates the unique instruction. Other than that, it should (tic) be pretty close.

Bobbias

Member

Exactly. I've never worked with modicon, so I wouldn't know what to mtell you to look for, but I'd assume there are some people who do stuff relying on the scan order... It's not that hard to come across a sitation where it might be advantageous to take advantage of that.

It's good that he came here asking before he tried to convert the code over and wondered why half of it wasn't working.

It's good that he came here asking before he tried to convert the code over and wondered why half of it wasn't working.

TConnolly

Lifetime Supporting Member

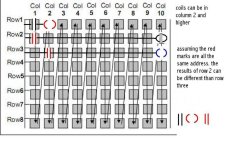

The thing you'll need to watch out for most are computations and block moves. For example, a block move in the network at r5,c2 will execute before an emath instruction at r2,c5, even though the emath instruction is at the top of the network. The execution order is essential because the block move is needed to set up the data in the registers for the emath instruction so it must execute first. Also keep in mind that even though an output instruction may appear in the right hand column, it's true solve column might be any column to the left, therefore an output at r7,c2 will solve before anything to the right and above of it, even though it appears to be in the lower right corner of the network. Depending on your logic this may or may not matter. To avoid any confusion over the actual sovle column, set your Proworx or Concept software to display the coils in the true solve column while you are translating the program. Be aware that power can flow up from bottom to top in a Modicon network. You may wonder how the processor handles certain functions, its helpful to know that a Modicon 984 remembers the state of everything from the previous scan while it solves the current scan, and then updates the previous scan image after the current scan has completed. Converting Modicon to AB is not difficult as long as you understand the scan differences.

Do you have a reference on the 984 instruction set? If you are using Proworx NXT or Proworx 32 then the online instruction help is the best reference there is, its better than the manuals. If you are working from a print out or some of the older software then you can download the logic block library manuals at http://forums.mrplc.com/index.php?autocom=downloads&showcat=25. The reference manual PDF files are way too big to post.

Proworx32 is buggy by the way - I think is suffers from ADD, if it appears to hang just wait a minute, eventually it will remember it is supposed to be doing something.

In the Modicon 984 the networks are divided by the user into sections and each section is scheduled for scanning. Its possible to schedule a section more than once per scan. There are no separate subroutines like you are used to in AB processors. Instead a section of code is left unscheduled and can then be treated as a subroutine with a subroutine call and return even though it will appear as part of one long monolithic program.

Do you have a reference on the 984 instruction set? If you are using Proworx NXT or Proworx 32 then the online instruction help is the best reference there is, its better than the manuals. If you are working from a print out or some of the older software then you can download the logic block library manuals at http://forums.mrplc.com/index.php?autocom=downloads&showcat=25. The reference manual PDF files are way too big to post.

Proworx32 is buggy by the way - I think is suffers from ADD, if it appears to hang just wait a minute, eventually it will remember it is supposed to be doing something.

In the Modicon 984 the networks are divided by the user into sections and each section is scheduled for scanning. Its possible to schedule a section more than once per scan. There are no separate subroutines like you are used to in AB processors. Instead a section of code is left unscheduled and can then be treated as a subroutine with a subroutine call and return even though it will appear as part of one long monolithic program.

Last edited:

milldrone

Member

Similar Topics

Hello all i have setup a few LANs with the PLC5/40 and the SLC5/05. These have been all stand alone networks with the computer at one ip addr and...

- Replies

- 2

- Views

- 1,673

Hello all is there someone out there that is proficent at converting modicon to allen bradley plc5. I have a water demineralizer from L*A water...

- Replies

- 8

- Views

- 2,710