You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Quick Question on PLC Ladder Logic Execution

- Thread starter mike64b

- Start date

Mickey

Lifetime Supporting Member

I just tried it on a ML1500. I used a OTL ( output Latch) instead of a JMP instruction and it executed. The OTL latched.

Mickey thanks so much for taking the time to check it out. I was worried that upon returning to the rung it would first re-evaluate the B3:2/5 XIO and if that was true do the JMP, but it seems it actually operates as I hoped!

Considering you tested this out, does that imply this rung example is not common? I hope I am not attempting things that are considered in the dark realm of ladder logic

Considering you tested this out, does that imply this rung example is not common? I hope I am not attempting things that are considered in the dark realm of ladder logic

TConnolly

Lifetime Supporting Member

If you ever have any doubt about how a rung will execute then double click on the rung number. The mnemonic instructions for the rung will appear. The rung will execute the instructions in exactly the order listed on the mnemonic line.

Last edited:

If you ever have any doubt about how a rung will execute then double click on the rung number. The mnemonic instructions for the rung will appear. The rung will execute the instructions in exactly the order listed on the mnemonic line.

I would have suggested exactly the same thing Alaric. Nice tip.

Anyone who has ever been on a Rockwell training course will have course material with diagrams that show the RET from a subroutine returning execution to the start of the next rung!

That is WRONG !! Execution continues from the right-hand side of the JSR, and if the next instruction is NXB, execution continues on the next branch down.

That is WRONG !! Execution continues from the right-hand side of the JSR, and if the next instruction is NXB, execution continues on the next branch down.

This makes sense to me... I'm glad it operates in this way as when I do a JSR I want it to return to exactly after that JSR and not do anything funny like re-run the rung.

Complete sense is made if you treat EVERY instruction as just "an instruction" - it doesn't matter what instruction it is, the remainder of the rung will be processed as normal.....

... an exception - JMP will jump to the specified label as it is encountered, no further processing will be performed on the rung.

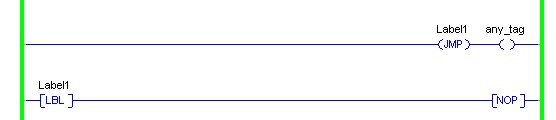

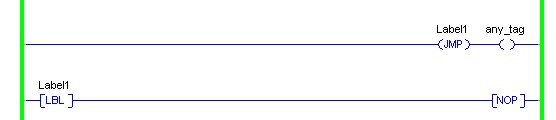

See the pic to understand this - there is no other reason why any_tag should not be true

... an exception - JMP will jump to the specified label as it is encountered, no further processing will be performed on the rung.

See the pic to understand this - there is no other reason why any_tag should not be true

Yep I see what you are saying, this operation follows what I would expect since I am used to C type and assembly language programming mostly. Ladder logic is very new to me.

Edit: Another quick question.. Any reason why labels cant just be a rung on there own without an output? Is it just do to the fact all rungs must have outputs? And can a workaround just be, for the rung with a label, to latch some internal bit that is never used?

Edit: Another quick question.. Any reason why labels cant just be a rung on there own without an output? Is it just do to the fact all rungs must have outputs? And can a workaround just be, for the rung with a label, to latch some internal bit that is never used?

TConnolly

Lifetime Supporting Member

In a ControlLogix processor you can use the NOP instruction (no operation) as Daba showed. Otherwise all rungs have to terminate with an output instruction. In your Micrologix you'll need to have a work around. One good one is just what you suggested, an OTE or OTU assigned an internal bit that isn't used. However there is not any reason that you can't just proceed with whatever logic is on the next rung right after the LBL on the same rung as your work around.

Note that also in your Micrologix you can't do what Daba showed with the JMP instruction. In the Micrologix case the OTE any_tag would be required on a branch below the JMP instruction. Despite that it would be jumped and not executed as Daba explained, leaving any_tag in its last state.

Note that also in your Micrologix you can't do what Daba showed with the JMP instruction. In the Micrologix case the OTE any_tag would be required on a branch below the JMP instruction. Despite that it would be jumped and not executed as Daba explained, leaving any_tag in its last state.

Last edited:

In a ControlLogix processor you can use the NOP instruction (no operation) as Daba showed. Otherwise all rungs have to terminate with an output instruction. In your Micrologix you'll need to have a work around. One good one is just what you suggested, an OTE or OTU assigned an internal bit that isn't used. However there is not any reason that you can't just proceed with whatever logic is on the next rung right after the LBL on the same rung as your work around.

Note that also in your Micrologix you can't do what Daba showed with the JMP instruction. In the Micrologix case the OTE any_tag would be required on a branch below the JMP instruction. Despite that it would be jumped and not executed as Daba explained, leaving any_tag in its last state.

Should have replied in MicroLogix context - apologies

Well now that I think about it, I am usually using the JMP to go to the end of an SBR and in that case I would just have the output condition as a RET on the label rung so thats not an issue.

That leaves the only issue in the main program LAD2 where if I want to jump to the end I wouldn't have anything on the output... I wonder is this an area where instead of using a JMP I would use TND to perform the I/O scan and restart the ladder scan from beginning?

That leaves the only issue in the main program LAD2 where if I want to jump to the end I wouldn't have anything on the output... I wonder is this an area where instead of using a JMP I would use TND to perform the I/O scan and restart the ladder scan from beginning?

TND just acts like the end of program file, its like the processor sees the END rung. It is not normal to use a TND in the main program file, TND is a debugging tool, and shouldn't exist in a finished program.

In a subroutine, I would program an "early return" = a conditional RET instruction if I didn't need to process any more code.

In the main routine, LAD2, I would NEVER EVER program anything to stop the rest of the code executing. Doing so makes any code added "position dependant".

It sounds like you are trying to tie your logic execution to the application - let the logic solve whatever is thrown at it.

In a subroutine, I would program an "early return" = a conditional RET instruction if I didn't need to process any more code.

In the main routine, LAD2, I would NEVER EVER program anything to stop the rest of the code executing. Doing so makes any code added "position dependant".

It sounds like you are trying to tie your logic execution to the application - let the logic solve whatever is thrown at it.

Last edited:

TConnolly

Lifetime Supporting Member

Similar Topics

I apologize for not having the model of the plc. I am trying to get it.

I have a print out of the program and it seems straight fwd.

One...

- Replies

- 12

- Views

- 3,432

What is the current cable to use to connect a laptop PC to a PLC-5 channel 0 (25 pin connector). I have a homemade cable that is just like...

- Replies

- 3

- Views

- 1,537

I have a solenoid powered off a 1756-OA16I. The output has a fuse and then runs off to the solenoid. Now I am not able to change the card at...

- Replies

- 4

- Views

- 1,430

Hi everybody i am currently working with a project at my company and i have spent mostly of the evening yesterday and the morning today trying to...

- Replies

- 8

- Views

- 4,014