Hello,

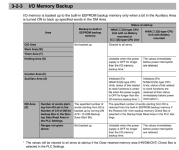

I want to understand the memory mapping of a CPE1 Omron PLC. Which areas are accessible and generally operate like a flag bit.

Second, Can we call the same output , say 100.0 in multiple subroutines?.

Sorry if this is trivial. New to OMRON programming environment.

I want to understand the memory mapping of a CPE1 Omron PLC. Which areas are accessible and generally operate like a flag bit.

Second, Can we call the same output , say 100.0 in multiple subroutines?.

Sorry if this is trivial. New to OMRON programming environment.