Nerdlinger

Member

Hello Everyone!

It has been a while since I used the method of drawing a state diagram, converting that to Boolean algebra, and translating that to a ladder diagram. I am hoping you can help with my erroneous method!

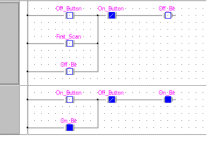

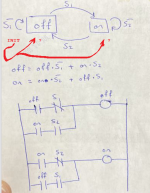

Please see the attached example. I started with a state diagram, with the state options being "on" or "off" and switching between the two via switches "S1" or "S2." I also added the loops where they will remain in their respective state if the switch that transitions the state to the next is NOT true/pressed. (I believe those loops ultimately gets translated to latches.) From there I wrote two algebraic expressions defining the "OFF" state and "ON" state. Finally, I used those expressions to draw the rungs of the ladder diagram. But something is off and here is where I need help:

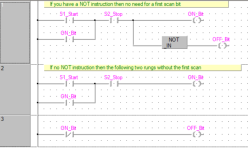

1. When the program first runs neither "OFF" nor "ON" outputs will be true, so they will never be able to get on! (Look at the first column.)

2. Lets say I program the "OFF" output to have an initial value of "true" upon starting the program. When I hit S1 to turn the machine on the "S1" contact in the 4th rung will close BUT the "OFF" contact right next to it will be open since rung 1 will be broken, even before rung 3 has a chance to latch the "ON" output on!

AH! What am I missing?

P.S. I know this example could be solved with the classic "START/STOP" circuit but I am really trying to remember how to use this method to ultimately arrive at something like the classic "START/STOP." Thank you!

It has been a while since I used the method of drawing a state diagram, converting that to Boolean algebra, and translating that to a ladder diagram. I am hoping you can help with my erroneous method!

Please see the attached example. I started with a state diagram, with the state options being "on" or "off" and switching between the two via switches "S1" or "S2." I also added the loops where they will remain in their respective state if the switch that transitions the state to the next is NOT true/pressed. (I believe those loops ultimately gets translated to latches.) From there I wrote two algebraic expressions defining the "OFF" state and "ON" state. Finally, I used those expressions to draw the rungs of the ladder diagram. But something is off and here is where I need help:

1. When the program first runs neither "OFF" nor "ON" outputs will be true, so they will never be able to get on! (Look at the first column.)

2. Lets say I program the "OFF" output to have an initial value of "true" upon starting the program. When I hit S1 to turn the machine on the "S1" contact in the 4th rung will close BUT the "OFF" contact right next to it will be open since rung 1 will be broken, even before rung 3 has a chance to latch the "ON" output on!

AH! What am I missing?

P.S. I know this example could be solved with the classic "START/STOP" circuit but I am really trying to remember how to use this method to ultimately arrive at something like the classic "START/STOP." Thank you!