If an element on a rung is false, does that shorten the scan time, as it does not need to execute anything on the rung after that?

similarly, if there is a jump to label, that is executed and the logic between them is skipped, does that shorten scan time?

thank you

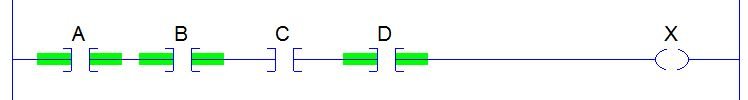

Your first question.... The program scan has to "execute"

each and every instruction on a rung, even if the Rung Logic Continuity (RLC) has been made false by a false conditional instruction. Many instructions "react" to the RLC being false, in the same way that many "react" to the RLC being true. Just making a rung false does not guarantee a faster execution time, it totally depends on what instructions the processor encounters after RLC goes false.

Having said that, there are guidelines for instruction placement that can improve scan time. Place instructions that have the highest probability of being false, and thus turning the RLC false, at the

beginning of a rung, subsequent conditional instructions do not have to interrogate the tag database, because the rung cannot be turned true again (branching obviously modifies this behaviour).... All the processor will be doing, once there are no open branches, is searching for instructions that it has to "react" to the RLC being false (e.g. OTE, TON, TOF, CTU, CTU, etc. etc.)

I could check, and so could you, the execution times for output instructions when the RLC is true, and when it is false. I'm guessing that nearly all execute faster when the RLC is false, but they must execute.

Your second question.... JMP to a (later) LBL will "skip" the code between them, so execution time will be faster, yes. But be aware that when you make the rung with the JMP true, all of the rungs between the JMP and the LBL will

not be scanned, so any "outputs" within that skipped logic will freeze, OTE's will stay on, even if the rung conditions dictate they go off.