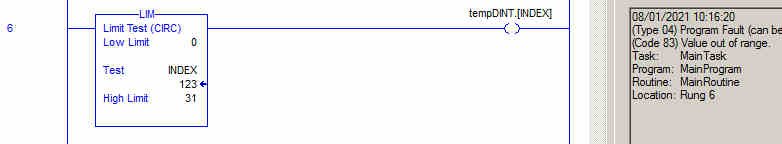

So it appears as though we have exposed a "bug" (which no doubt RA will undoubtedly call a "feature", say it was deliberate, and try to give an explanation why - should be interesting !).

But I have only tested this on Firmware Revision 20.

If anyone can oblige with the same test I did at the latest firmware revision, it would infer that it has always been there, and without an RA fix, it will always be.

I should not have to say this - don't do this on a running, live, active controller in the real world, indications are that bit-level indirection will most likely fault the controller !

This is not mitigation, but it is fair to say that not many people use BOOL Arrays, for the simple fact that there is not a lot you can do with them, other than for storage or HMI/SCADA exchange. Perhaps this is a reason why this "enhanced undocumented feature" has been hidden for so long.

But if we can get proof that this still exists in the latest firmware, then a shout at RA from someone with T/C might get the ball rolling for a "correction" in future firmwares.

But I have only tested this on Firmware Revision 20.

If anyone can oblige with the same test I did at the latest firmware revision, it would infer that it has always been there, and without an RA fix, it will always be.

I should not have to say this - don't do this on a running, live, active controller in the real world, indications are that bit-level indirection will most likely fault the controller !

This is not mitigation, but it is fair to say that not many people use BOOL Arrays, for the simple fact that there is not a lot you can do with them, other than for storage or HMI/SCADA exchange. Perhaps this is a reason why this "enhanced undocumented feature" has been hidden for so long.

But if we can get proof that this still exists in the latest firmware, then a shout at RA from someone with T/C might get the ball rolling for a "correction" in future firmwares.