I can't watch the video right now to see what is said, but I would expect this logic to function as you describe (on then off, staying off).

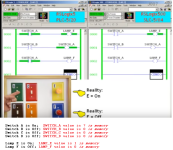

It looks to me like this is intended to demonstrate how latching bits in sequence works with OTEs:

1. When you first push the button M0 becomes true, and is then latched in permanently*.

2. When the button is released M1 becomes true and is latched until M0 becomes false (which can't happen via the logic)

3. When the button is pushed a second time M2 becomes true and is latched until M1 becomes false (which only happens if M0 becomes false, which can't happen)

4. The output is on when M0 is true and M2 is false (see above steps to determine that this becomes the case at 1 and stops being the case at 3)

5. Thereafter pushing the button will result in I:0/0 changing state but nothing else, as all the internal bits are stuck on.

* 'permanently' in this case meaning until you either toggle it off manually or the processor leaves and re-enters run and the prescan turns it off.

Compare what happens if you add an XIO for M2 to the beginning of rung 0 and ask yourself why the result is different.