TL;DR

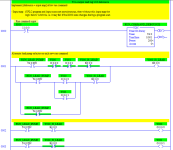

@parky's solution is the right answer for the OP:

Whether to add a debounce and/or an input map depends on the hardware.

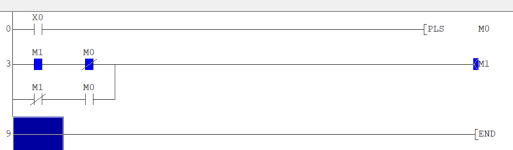

However, someone searching for lead/lag in the future and finding this thread, but having a PLC that does not have the ALT instruction, cannot use that solution as written. The alternative is to use a flip-flop circuit for the first rung above [XIC X000 ALT M0]:

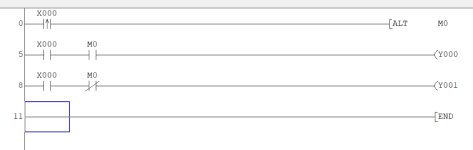

Code:

X000

----] [---------------------[OSR ]---

[Storage X000_store]

[Output X000_rising_edge]

X000_Rising_Edge M0 M0

--+------] [------------]/[------+------( )---

| |

| X000_Rising_Edge M0 |

+------] [------------] [------+

N.B. A-B ladder used for the OSR [one-shot rising] instruction; some other OEMs do not have the --]^[-- instruction, as in rung 0 of @parky's example.

N.B. X000_Rising_Edge is only true for one scan i.e. in A-B parlance it is the output of a one-shot.

EvenLonger;DR

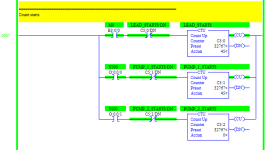

Laying in bed thinking about this (yeah, I gotta get a life

), I wondered if the Y000/Y001 states could be a proxy for the storage bit of the one-shot determination, and came up with this hot mess:

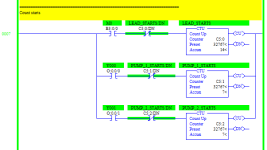

Which is at least cleaner than the original, even hotter mess: