There are some programs that have multiple latch instruction on the same rung of logic when RS Logix 5000 is the development software. The RS Logix 500 doesn't allow this type of programming. If a person encounters many latch bits in one rung of logic how is this type of code executed. I rarely encounter this approach to programming in the RS Logix 5000 software.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

multiple latch bits in series rs logix 5000

- Thread starter floyd2904

- Start date

The latching happens in the same rung, this means that the bits are set to TRUE for all the OTL instructions at the end of that rung.

If an examine ON(XIC) is placed on the next rung, the rung out condition would be TRUE for the XIC.

Multiple OTL per line just enable a shorter amount of code, since we can now do this:

XIC(Condition1) OTL(Output1)OTL(Output2)OTL(Output3)

Instead of

XIC(Condition1) OTL(MemoryBit1)

XIC(MemoryBit1)OTL(Output1)

XIC(MemoryBit1)OTL(Output2)

XIC(MemoryBit1)OTL(Output3)

If an examine ON(XIC) is placed on the next rung, the rung out condition would be TRUE for the XIC.

Multiple OTL per line just enable a shorter amount of code, since we can now do this:

XIC(Condition1) OTL(Output1)OTL(Output2)OTL(Output3)

Instead of

XIC(Condition1) OTL(MemoryBit1)

XIC(MemoryBit1)OTL(Output1)

XIC(MemoryBit1)OTL(Output2)

XIC(MemoryBit1)OTL(Output3)

RSLogix 5/500 only allowed output operations to be the last instruction, which had the effect of limiting logic to a single output on each rung/branch.

5000 changes this to a limitation that the last instruction of the rung must be an output, but the basic operation remains unchanged -- the rung is evaluated up to the point of the instruction and then the output instruction performs any operation based on the rung state (in the case of an OTL/OTU, it will do nothing if the rung is false and turn a bit on/off if true). The program will then continue on to the next instruction in the rung and evaluate that.

Note that output instructions do not alter the state of the rung as it is being evaluated -- if the rung evaluates to false prior to an output instruction, it is still false afterward, and if it is true before it will be true afterward.

You can also mix input and output instructions (although this is generally not recommended to avoid confusing people not used to the format).

5000 changes this to a limitation that the last instruction of the rung must be an output, but the basic operation remains unchanged -- the rung is evaluated up to the point of the instruction and then the output instruction performs any operation based on the rung state (in the case of an OTL/OTU, it will do nothing if the rung is false and turn a bit on/off if true). The program will then continue on to the next instruction in the rung and evaluate that.

Note that output instructions do not alter the state of the rung as it is being evaluated -- if the rung evaluates to false prior to an output instruction, it is still false afterward, and if it is true before it will be true afterward.

You can also mix input and output instructions (although this is generally not recommended to avoid confusing people not used to the format).

Operaghost

Member

Operaghost

Member

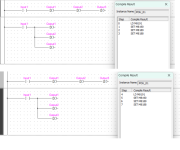

Another example of what you can do now. These two rungs also perform the same function and will execute the same. But perhaps this is also an example of when maybe you shouldn't use a new capability! The bottom rung tends to make people confused. And if you have a problem on a production line, you don't want confusing code.

OG

OG

drbitboy

Lifetime Supporting Member

The latching happens in the same rung, this means that the bits are set to TRUE for all the OTL instructions at the end of that rung.

If an examine ON(XIC) is placed on the next rung, the rung out condition would be TRUE for the XIC.

Multiple OTL per line just enable a shorter amount of code, since we can now do this:

XIC(Condition1) OTL(Output1)OTL(Output2)OTL(Output3)

Instead of

XIC(Condition1) OTL(MemoryBit1)

XIC(MemoryBit1)OTL(Output1)

XIC(MemoryBit1)OTL(Output2)

XIC(MemoryBit1)OTL(Output3)

There is a typo there, and those two examples are not equivalent, but I think the point made is basically correct.

In traditional PLC ladder it was assumed that output coils could only be put at the right most i.e. end of rung, this stems from traditional relay logic, however, even in traditional relay logic (although relay coils could not generally be seriesed) it was often a done practice to have contacts in the cold side of the relay coil, even some where other coils were also connected via the cold side leg reducing the need for extra contacts. With the newer function block diagram etc. there was a change to allow many cobinations i.e. coils before & after logic because a PLC "coil" does not need a voltage near to it's designed operating parameters unlike a relay. also stemming from that is FBD where a function has an EN & ENO pin so if the EN (Enable pin) is true then the ENO (output pin) is also true. I worked with a development engineer who designed their own PLC system specifically for their own systems, the software was indeed FBD with built in functions this was way before the introduction of the IEC programming, so although it probably was a loss leader he was far ahead of his time in PLC programming logic, it was not until some time later when the newer IDE's came out did I realise the significance of this type of structured programming

There is a typo there, and those two examples are not equivalent, but I think the point made is basically correct.

Is the typo the extra space? Can't figure it out maybe I rely a little too much on code verification

Also, functionally, is it different because the memory+CPU Time consumption is different? Otherwise the functionality seems to be the same right?

Also, functionally, is it different because the memory+CPU Time consumption is different? Otherwise the functionality seems to be the same right?

Consider the situation in which Condition1 becomes true (latching all outputs), then becomes false and remains so. What happens in each scenario if an output is then toggled off, say by a momentary OTU?

In the shorter logic the toggled output turns off and remains off.

In the longer logic, it will be set to true again the next cycle because MemoryBit1 is latched in.

The actually equivalent logic would have MemoryBit1 as an OTE, not an OTL.

drbitboy

Lifetime Supporting Member

+1consider the situation in which condition1 becomes true (latching all outputs), then becomes false and remains so. What happens in each scenario if an output is then toggled off, say by a momentary otu?

In the shorter logic the toggled output turns off and remains off.

In the longer logic, it will be set to true again the next cycle because memorybit1 is latched in.

The actually equivalent logic would have memorybit1 as an ote, not an otl.

Similar Topics

This is the first time I am working with Simatic Manager Step7 as I started my siemens journey with TIA which is pretty easy and do a lot of stuff...

- Replies

- 3

- Views

- 146

Compactlogix controller, program has 28 conveyors that use TON's to start the conveyors. The TT sounds a warning horn during start and the DN...

- Replies

- 10

- Views

- 496

I have 9 field devices, three METSEPM5110 power meters and six ACE949-2 rs285 interface modules. I want to read this Modbus rtu data through rs485...

- Replies

- 8

- Views

- 317

I'm trying to use DTM browser to make make modbus poll from RTAC. I'm able to get the points in first poll object. But not able to get anything in...

- Replies

- 1

- Views

- 127

Hello, I encountered a problem with the kinetix 6500 drive, error code s22, loss of 3 phase voltage. After disassembling and replacing the thermal...

- Replies

- 2

- Views

- 170