Allen,

The latch is reset on a first scan so I also need on the unlatch to be able to latch a reset bit which is why I've used a latch and unlatch.

Hope that makes sense

The latch is reset on a first scan so I also need on the unlatch to be able to latch a reset bit which is why I've used a latch and unlatch.

Hope that makes sense

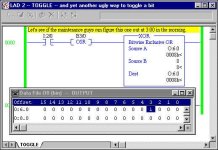

I:1/0 B3/0 ---------------

|------] [-----[OSR]-------|CTU |----(CU)---|

| |Counter C5:0 | |

| |Pre 2 |----(DN)---|

| |Acc 0 | |

| --------------- |

| --------------- O:2.0 |

|------|EQU |-------------------------(L)---|

| |Sour C5:0.acc| |

| |Sour 1|

| --------------- |

| --------------- O:2.0 |

|------|EQU |-------------------------(U)---|

| | |Sour C5:0.acc| | | |

| | |Sour 2| | | |

| | --------------- | | -------------- |

| | First scan | |---|MOV |--|

| ------] [------------ | |Source 0| |

| | |DestC5:0.acc| |

| | -------------- |

| | |

| -------------(L)----|